►

From YouTube: AWG / MOS-AK panel working group

Description

Silicon modeling panel discussion

A

A

C

B

C

A

C

A

C

C

C

F

C

Yeah

Eric

I,

don't

I,

don't

know

because

vladic

was

vladic

was

always

listed

as

a

as

a

panelist

and

so

were

some

of

the

others.

So

I

I

really

don't

know

why

there

are

some

of

these

discrepancies

with

the

zoom

so

to

speak,

but

thankfully

able

to

revise

these

here

on

the

fly.

So

that's

that's

good

news,

yeah

and

I

want

to

thank

all

the

panelists

for

making

time

to

come

today

and

also

for

the

audience

for

I

think

what

will

be

a

very

informative

session.

A

So

good

morning,

I'm

really

glad

seeing

outstanding

lineup

of

panels

today

and

growing

list

of

attend.

This

short,

it

will

be

a

very

informative

discussion

and

presentation

about

modeling

simulation

and

I

see

designing

particle

using

open

source

free

pdk

from

Sky

water

and

I.

Guess

there

was

a

request

to

slightly

change

agenda

and

I

think

did

you

Kevin

asked

to

be

first

because

of

your

time,

I.

A

Maybe

maybe

we

can

start

with

with

your

talk,

it's

a

update

on

standardization

efforts

and

I'm

sure

this

would

be

of

your

interest

and

then

we

will

or

right

onto

the

presentation

of

smooth

schedule.

So,

let's,

let's

begin

with

first

presentation

by

Kevin

on

his

contribution,

though

I

could

please

standardization

efforts.

Yeah.

H

H

H

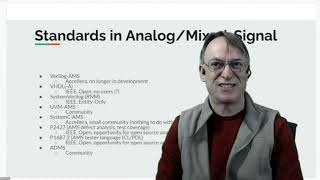

I

moved

on

from

that

and

into

verilog

EMS

in

the

90s

and

90s

there

was

Cadence

and

there

was

it

analogy:

we're

trying

to

standardize

what

they

had

in

languages

and

kids.

His

Specter

stuff

became

very

loggy

essentially,

and

the

other

effort

became

vhdle

I'm,

not

really

sure

if

anybody

uses

vhdla,

but

it's

it's

still

there

and

has

the

advantage

of

being

an

IEEE

open

standard.

So

anybody

can

participate

in

vhdl

stuff

if

they

wanted.

The

IEEE

prologue

EMS

should

have

combined

with

verolog.

H

Ies

came

in

that

was

actually

super

long

at

accelera

and

they

sort

of

forced

the

way

through

to

IEEE,

without

incorporating

very

long.

Ems

and

Cadence

were

dragging

their

feet

on

the

thing

so

system

burolog

ended

up

at

IEEE

and

verlog

EMS

kind

of

got

abandoned

at

accelera

and

sort

of

he

sort

of

ran

along

until

you

know,

somewhere

around

2014

or

something

where

there

was

a

sort

of

a

final

version

with

some

broken

stuff

in

it.

H

So

it's

a

system

verolog

arrived

at

the

same

level

as

vhdl

with

user-defined

types

A

few

years

ago,

but

has

the

same

problem

as

vhdl

that

they

have

not

been

able

to

work

out

how

to

get

multiple

types

on

a

net

and

getting

multiple

types

in

a

net

is

where

the

mixed

signal

stuff

comes

in.

So

we've

already

done

multiple

types

on

that

with

only

two

types

logic

and

analog

and

verolog

EMS.

So

what

I'm?

H

Currently,

working

on

is

trying

to

get

the

verilog

AMS

stuff

brought

into

system

error

log

and

make

make

that

work

for

any

kind

of

types

on

a

net.

The

the

problem

there

is

usually

the

the

system.

Burolog

standard

is

entity

only

so

mostly

the

Eda

vendors

playing

there

and

they

don't

actually

like

changing

their

software

much

so

so.

Basically,

you

need

to

pack

the

Committees

with

people

who

are

interested

in

actually

having

it

work

in

order

to

get

things

through.

H

Particular

it's

set

off

in

sort

of

the

wrong

direction

and

is

not

not

adjusting,

but

we

could

actually

fix

that

one

in

open

source

space

and

and

then

bring

it

back

in

as

a

phase

two

p247

thing,

if

one,

if

people

want

to

do

that,

p6087.2

was

doctored

by

the

same

people

as

2427.

It's

about

doing

stuff

in

analog

test.

One

of

the

things

about

analog

is

unlike

digital.

H

You

really

need

to

simulate

it

to

see

if

it's

going

to

work

so

there's

an

opportunity

in

simulating

testers

and

and

running

your

test

languages

on

the

simulation

to

see

how

things

go

and

again,

the

the

easy,

easy

sort

of

entry

point

for

this

stuff

is

sort

of

edms

which

is

common

to

everybody.

And

this

is

where

the

modeling

stuff's

coming

in

I'm

saying

the

opportunities.

H

Oh,

this

works

right.

You

know

things

I

think

people

are

interested

in

is

how

do

we

apply

AI

to

to

Eda

stuff

and

I'm?

Looking

at

like

a

lot

of

the

mixed

signal,

stuff

I

see,

you

know

the

math

and

the

event

driven

stuff

looks

like

neural

networks,

so

so

I'm

looking

at

a

lot

of

people,

building,

AI

accelerators,

which

basically

neural

network

math

machines,

which

could

equally

all

work,

as

you

know,

as

mixed

signals

simulation

machines.

H

There

is

it's

multi-vendor,

so

you

you

can't

just

use

Cadence

tools

or

synopsis

tools

or

Mentor

tools,

and

that

creates

an

opportunity

for

doing

sort

of

large-scale,

Open,

Source

stuff,

so

I'm.

Looking

at

you

know,

can

we

build

multi-simulator

systems

for

developing

chiplet

systems

and

optimizing

them

and

get

people

like

Facebook

and

Microsoft

to

back

that

effort

anyway?

That

was

one

where

we're

we're

trying

to

do

Hardware

software

co-design

and

with

AI

at

ocp

and

the

chiplet

stuff

and

high

performance

compute.

H

If

anybody

wants

to

hop

in

there

and

join

the

effort,

what

I

would

like

to

get

to

with

that

stuff

is

to

be

able

to

do

asynchronous

logic

rather

than

RTL.

That

again

requires

mixed

signal

simulators

rather

than

the

discrete

simulators

and

then

can

we

can

we

get

above

the

RTL

level

and

design

at

the

neural

network

level,

sort

of

asynchronous

FSM.

So

that's

that's

a

quick

summary

of

where

I'm

at

so.

If

anybody's

got

any

questions,

go

for

that.

H

Yeah

I

would

say

the

The

Proposal

I've

got

in

at

the

system.

Burolog

thing

at

the

moment

is

that

when

you're

trying

to

do

parallel,

processing

simulation

the

thing

that

you

want

to

communicate

between

the

simulators,

you

know

whether

it's

their

the

same

simulator

or

different

simulators

is

drivers,

not

signal

values.

H

So

none

of

the

Eda

vendors

do

that

stuff,

so

I

think

there's

an

opportunity

for

sort

of

high

performance,

Computing

simulation

stuff

with

open

source.

That's

fairly

easy

to

get

at

part

of

my

proposal

for

system.

Burolog

is

just

a

sort

of

high

level

methodology

for

doing

things,

and

you

know

be

interested

in

sort

of

filling

in

an

API

that

will

work

for

like

NG

spice

Zeiss.

H

J

H

So

the

way

this

thing

the

proposal

I've

got

at

the

moment

is

that

if

you

look

at

how

the

the

simulators

work,

they've

got

drivers

for

Nets

and

then

there's

receivers

and

I

did

a

thing

for

Zeiss

for

I

was

pulling

out.

Piecewise,

linear

signals

and

feeding

them

into

the

digital

simulator

and

back

and

and

the

the

sort

of

picture

you

want

is

that

for

all

the

simulators

involved,

there's

a

driver

with

a

waveform

and

the

waveform

is

kind

of

your

pwl

thing

and

there's

a

receiver

somewhere

else.

H

So

the

waveform

and

you're

trying

to

sort

of

get

values

from

one

to

the

other

and

within

the

system

dialogue

environment,

we're

trying

to

get

it.

So

we

can

do

driver

access

like

viralog

EMS.

So

you

can

see

that

waveform

and

then

you

can

use

VPI

or

pli

or

DPI

to

get

it

out

into

your

your

analog,

simulator

I've

done

a

couple

of

Integrations

with

you

know:

digital

simulators

and

spice

simulators

in

the

past.

H

So

it's

really

not

that

hard

It

just

fits

in

with

the

pwl

source

stuff

and

that

that's

part

of

the

proposal

to

system

verolog,

because

they're

trying

to

get

to

UVM,

EMS

and

they're

trying

to

get

to

system

C

AMS,

so

so

they

they

might

go

for

supporting

whatever,

whatever

I'm

trying

to

do

in

some

way.

If

anybody,

if

anybody

is

an

entity

company

member

of

IEEE,

if

you

turn

up

for

like

four

meetings,

you

get

to

vote

on

things.

The

only

downside

at

the

moment

is

on

the

system.

H

I

mean

the

idea

here

is

that

if

you

know

the

connect

module

stuff

in

very

long,

EMS,

I

I

invented

that,

like

in

95.,

so

basically,

what

we're

trying

to

do

in

the

moment

is

say:

okay,

let's

just

do

connect

modules

in

some

form

in

system

dialogue

and

a

connect.

Module

is

basically

just

a

module.

So

anything

you

can

do

in

a

module.

H

I

think

I

think

one

of

the

things

I

would

Zeiss

is.

You

know

it'd

be

nice

if

we

could

do

stuff

where

we

can

hack

at

the

circuit

as

we

go

so

some

ability

to

restart

and

that's

right-

the

p2427

stuff

comes

in.

If,

if

we

can

do

the

defect

and

there's

just

our

market

for

this

defect,

analysis

and

coverage

stuff

and

if

we

could

get

Zeiss

to

do

that,

then

we'd

probably

have

quite-

and

it's

not

hard

to

do

that.

One,

because

I

think

you

can

probably

switch

models

while

you're

running.

H

But

p2427

is

a

good

opportunity

and

also

the

1687.2

stuff.

It's

just.

Those

committees

needs

better

Direction,

but

there's

there's

definitely

pars

there.

You

can

leave

religion

and

say:

okay,

we

can.

We

can

make

our

tools

do

this

and

we

can

also

start

our

own

powers

IEEE

for

doing

things

and

just

create

our

own

standards.

H

Yeah,

so

it's

so

if,

if

you

know

how

the

simulators

work,

you

know,

Eric

can

probably

talk

about

this

more

you

know.

Space

simulators

are

the

large

Matrix

math

thing

a

fast

space

simulator

tends

to

be

small,

Matrix

math,

PCS

switching

or

are

the

hard

pieces

and

then

lots

of

event

driven

stuff

between

those.

H

So

so

something

like

you

know

what

we're

shooting

for

with

very

low

EMS

is

you

you

have.

You

know

accurate

models

of

analog

things,

you

know

event

driven

models

of

digital

things

and

you're

mixing

those

together.

That

looks

a

lot

like

a

neural

network.

You've

got

layers

such

past

messages

between

and

then

there's

Matrix

math.

H

So

my

in

my

main,

you

know

very

long.

Ems

would

be

a

perfectly

good

language

for

describing

a

neural

network.

You're

doing

a

shorthand

for

the

math

in

there

circuits

are

circuits.

Don't

really

need

a

lot

of

precision

in

the

models

which

is

like

neural

network

stuff,

they're,

always

trying

to

cut

down

the

the

size

of

the

mayor.

H

F

So

there

I

will

comment

that

there's

a

there's,

a

whole

field

of

research

in

you

know

physics

and

form,

neural,

Nets

and

attend.

You

know

people

attempt

to

discover

models

by

from

data

and

a

lot

of

you

know,

depending

on

what

sort

of

activation

functions

you

use

and

stuff

like

that.

Neural

Nets

can

often

resemble

a

discretized

differential

equation,

and

so

we've

done

a

bit

of

research

in

that

area.

F

My

Talk's

not

really

about

that,

but

we

have

a

we've,

had

a

couple

projects

at

San

Diego,

where

essentially,

we

often

have

some

weird

physics

we

need

to

model

and

it

takes

forever

for

the

physicists

to

figure

out

a

model

for

it

and

we

have

data,

and

so

if

we

can

just

sort

of

take

the

data

and

then

apply

some

data-driven

technique

like

neural

Nets

to

it

and

create

a

model

quickly.

That's

a

big

win.

Yeah.

H

H

G

H

H

F

A

G

A

F

I

F

G

I

G

F

F

F

You

know

they've

they've,

basically

created

a

set

of

files

that

are,

you

know

for

one

of

the

two

common

commercial

simulators

and

the

main

two

are

age,

spice

inspector,

and

so

you

know

for

another

simulator

to

be

compatible

with

a

pdk.

That

means

that

you

really

need

to

be

compatible

with

the

you

know,

the

the

net

bus

languages

of

at

least

one

or

possibly

both

of

those

commercial

simulators,

and

so

that

actually

implies

lots

of

things.

F

You

know

you

have

to

have

all

of

the

right

device

models

available.

You

have

to

have

all

of

the

right

analysis

types

available

that

somebody

might

want

to

use.

You

have

to

have

good

expression

support.

You

have

to

support

the

same

syntax,

hopefully

you'll.

You

know

some

of

these

modern

pdks

are

really

complicated,

so

you

need

to

have

a

parser

that

performs

pretty

well

and

can

digest

the

massive

number

of

files

that

a

pdk

might

have

and

do

it

fairly

quickly.

F

So

I'll

be

talking

about

all

of

that

to

the

extent

that

I

have

time

and

I'll

give

a

little

bit

about

what

zeiss's

current

status

is,

is

a

fairly

important

priority

for

us.

Now,

although

it

hasn't

always

been

so,

as

some

of

you

may

be

familiar

with

zeites,

we

started

writing

Zeiss

a

little

over

20

years

ago.

F

F

One

sort

of

intermediate

thing

that

worked

on

as

a

atlas

translator

that

we

call

XDM

and

I'll

talk

about

that

a

little

bit

later.

Another

thing

that's

new

to

Zeiss.

That

was

we

were

just

discussing

in

the

last

talk.

Is

we

have

a

python

model

interface

which

allows

people

to

do

to

develop

ml

based

models?

You

know

using

tensorflow

or

pytorch

or

whatever

Library

they

want

in

Python

and

then

to

actually

execute

those

models

synthesize

that

list

and

just

call

them

from

there.

F

F

Maybe

we

could

use

a

database

method

to

develop

models

using

ml,

so

we've

had

a

few

or

we

have

a

few

ongoing

research

projects

on

that

topic,

see

other

things

about

Zeiss

we've

been

open

source

since

2013,

starting

with

like

6-0

we're

under

the

GPL

version

three

license.

Our

most

recent

release

was

7.6

that

happened

last

month

November

and

we're

trying

to

do

releases

every

six

months,

but

also

you

know

if

people

are

impatient

and

they

want

to

get

code,

changes

that

happen

in

between

releases

we're

also

GitHub.

F

F

So,

like

most

spice

emulators,

we

support

a

lot

of

the

standard

analysis,

types

that

you

see.

Anxiet,

noise,

AC

Etc,

there's

a

number

of

slightly

slightly

more

exotic

methods.

We

also

support

like

harmonic

balance

and

adjoint

sensitivities

and

polynomial

chaos

methods.

Those

I

think

are

a

little

more

unusual,

at

least

in

the

open

source

domain,

but

mostly

I

mean

most

of

the

sort

of

standard

techniques

are

what

people

who

are

running

pdks

with

wine

use.

F

So

we

do

have

support

for

those

I'm

going

to

say

a

little

bit

about

zeiss's

parallelism

and

mostly

to

sort

of

set

some

context

for

some

of

the

parsing

discussion.

So

there's

sort

of

three

parts

of

the

problem.

So,

on

the

right

hand,

side

you

have

a

flow

chart

showing

what

a

transient

simulation

of

Zeiss

would

do

or

any

simulator

would

do.

F

There's

sort

of

a

nested

set

of

solvers.

So

there's

a

time:

integration,

Loop,

there's

a

nonlinear

solver

inside

of

that

Loop

and

then

there's

a

linear

solver

inside

of

that

Loop

and

before

all

that

happens,

you

have

to

set

up

the

problem

and

that's

where

netlist

parsing

comes

in

and

so

I

think.

For

a

long

time

we

really

only

focused

on

optimizing

the

device

evaluation

and

when

you're

solved

parts

of

the

problem

and

that's

those

are

the

two

boxes

inside

of

the

loop

there.

F

But

we've

also

seen

performance

issues

and

parsing,

so

even

to

digitalize

that,

as

we

possibly

can

and

actually

the

parallel,

the

parallelism

that

we

apply

to

device

evaluation

actually

starts

during

parsing,

because

the

essentially

well

I'll

get

to

this

in

the

next

slide.

But

but

basically

we

try

to

distribute

devices

before

they're

even

fully

set

up

and

then

and

then

allow

as

much

of

the

setup

to

happen

on

all

the

individual

processors

as

possible.

F

F

F

We've

applied

subsequently,

where

we

try

to

wait

devices

based

on

how

expensive

they

are

so

so

we

also

can

do

device

waiting,

but

all

of

that

is

sort

of

determined

actually

during

parsing,

because

we

don't

even

want

to.

We

don't

even

want

to

set

the

devices

up

before

they're

communicated

we

just

want

to.

We

just

want

to

send

tokens

describing

the

device

to

each

person.

So

that's

where

the

parsing

comes

in.

F

F

It's

basically

flexing

and

parsing

things

that

don't

really

have

a

parallel

distribution,

so

either

stuff

that's

needed

on

products

only

on

proc0

or

stuff,

that's

needed

on

every

processor

and

then

we're

also

Gathering

statistics

on

that

pass

to

help

figure

out

how

to

do

the

parallel

Distribution

on

the

second

pass,

and

so

on.

The

second

pass,

and

basically

we

know

how

many

devices

there

are

going

to

be,

and

we

know

how

we

want

to

distribute

them

and

so

on

that

pass.

F

Then

we

just

do

some

sort

of

minimal

licensing,

and

then

we

pass

the

tokens

around

to

all

of

the

different

all

the

different

processors

and

after

the

tokens

arrive

at

the

different

processors,

then

the

rest

of

the

parsing

happens

and

the

rest

of

the

device

set

up

maps.

So

partly

for

this

reason

it's

been

you

know,

because

the

parallelism

is

kind

of

embedded

in

it.

That's

made

sort

of

refactoring.

The

purse

are

kind

of

kind

of

difficult.

F

So

what

we're

gonna

do

some

in

the

near

future

is

replace

the

Lexington

parsing

phases

with

a

much

more

modern

style

watching

in

person,

and

that

should

enable

us

to

apply

different

grammars

a

lot

more,

a

lot

more

easily,

so

I'm

going

to

revisit

this

in

a

minute.

But

that's

that's

basically

the

general

idea,

so

here's

kind

of

a

high

level

slide

about

zeiss's

compatibility.

F

So

we've

kind

of

taken

a

two-pronged

approach

to

that

one

is,

is

to

continue

hacking

on

our

on

the

existing

parser

to

get

it

as

close

as

possible

to

h-spice,

because

zeiss's

syntax

is

not

too

different

than

h-vice

and

we

have

a

command

line

option

that

sort

of

enables

all

the

h-spice

related

syntax

that

we

can

that's

available.

The

other

approach

has

been

to

do

something

more

comprehensive.

We

want

to

like

I

mentioned

before.

We

want

to

replace

the

Lexi

and

parsing

phases

in

science

with

something

more

modern

inside

the

department

tool.

F

First

and

so

we've

been

developing

a

code

called

the

Zeiss

data

model

or

XDM,

and

that

one

actually

uses

a

more

modern

parser

generator.

It

uses

the

the

Boost

Spirit

parser

generator,

and

so

we

have

grammars

worked

out

for

several

different

file

formats.

Now,

right

now

it's

a

standalone

tool

which

basically

converts

net

lists

and

pdks

from

whatever

format

they're

in

into

something

that

Zeiss

can

can

run.

F

Let's

see

another

element

that

we've

had

to

work

on

and

I'll

talk

about

this

on

the

next

slide,

since

we've

had

to

completely

rewrite

the

expression,

library

and

I'll,

explain

why

that

is

in

a

minute

and

then

also

in

order

to

support

modern

industry

standard

models.

We've

been

using

the

adms

neurologic

model.

F

It

has

been

fairly

I've,

been

I've,

been

successful

in

getting

undisclosure

agreements

set

up

with

global

boundaries

in

the

past.

I

have

not

been

successful

with

gsmc,

so

so

that's

one

reason

you

don't

see

very

many

tsmc

pdks

listed

here

the

and

that's

also

a

reason

why

I'm

pretty

happy

to

see

there's

this

move

towards

open

sourcing

pdks,

because

that

just

makes

collaboration

a

lot

easier.

F

F

News

12

liter

PK

that

particular

pdk

had

enough

enough

expressions

in

it

enough

parameters

in

it

that

we

were

getting

expression,

trees

that

were

really

really

big

and

because

of

a

fundamental

design

flaw

in

the

old

expression

Library

there

there

I

think

there

was

like

an

an

end

to

the

third

sort

of

search

in

it

or

something

like

that

anyway.

So

there

was

something

in

it

that

was

really

really

inefficient,

and

so

we

had

to.

We

basically

had

to

make

a

change

and

we'd

had

a

lot

of

complaints

about

the

old

expression

Library.

F

So,

like

the

example

I'm,

giving

here

is

a

vco

circuit,

I

think

that

was

the

first

circuit.

We

tried

to

run

and

it's

like

7.1

using

the

old

library

I.

Just

it

just

never

got

past

person

and

with

z72.

Not

only

does

it

get

past

person,

it

runs

the

whole

thing

in

about

20

seconds.

So

it's

a

it's

a

pretty

big

Improvement,

let's

see

I

guess

at

the

bottom

here,

I'm

also

talking

quite

a

bit

about.

F

In

addition

to

expression,

libraries

there's

also

been

a

lot

of

improvements

in

the

Purser

performance.

Mostly

that's

had

to

do

with

just

making

much

better

use

of

hash

maps

and

much

better

use

of

not

storing

things.

We

don't

need

to

store

a

lot

of

times

when

you're

using

a

pdk,

there's

a

lot

of

parameters

that

aren't

actually

used

by

the

particular

circuit

that

you're

running,

so

we

throw

those

away

as

quickly

as

we

can.

F

Let's

see,

I

also

mentioned

model.

Compiler

is

a

very

important

to

be

able

to

run

all

of

the

industry

standard

models.

You

know

there's

a

handful

of

standard

devices

that

that

modern

pdks

tend

to

use

like,

for

example,

the

BSN

CMG

model,

and

the

way

we

get

that

in

designs

is

using

the

adms

model.

Compiler.

F

One

thing

we

discovered

when

we

started

running

with

the

decent

CMG

was

that

the

the

code

that

we

were

producing

precise

from

adms

was

extremely

slow

and

I

was

largely

because

the

eight

automatic

differentiation

library

that

we

were

using

was

was

slower

than

we

thought,

and

so

we

completely

rewrote

the

way

that

we're

doing

ad

in

the

back

end

of

adms,

and

that

resulted

in

now

in

code.

That's

about

as

fast

as

handwritten

code.

So

we've

had

a

really

significant

speed,

improvement

from

that

and

and

basically

that

was.

F

I

will

mention

that

adms

it's

been

around

for

a

long

time

and

we

were

happy

to

use

it,

but

I

think

we're

getting

to

a

point

where

I

think

we

want

to

try

to

use

something

else,

and

so

we're

sort

of

taking

two

approaches

here.

One

is:

is

that

there's

a

there's,

a

new

open

source

model,

compiler

called

openvaf,

and

so

we're

looking

at

that,

but

we're

also

internally

developing

our

own

model

compiler,

so

at

some

point,

that'll

become

available

and

that

hopefully,

will

work

a

little

better.

F

The

main

problem

that

we

have

with

adms

is

that

it

doesn't

support

everything

in

the

the

verilogy

standard

and

it's

fairly

hard

to

hack

on

it

to

to

add

features

to

it.

So

so

that's

another

activity,

oh

I,

wanted

to

make

a

few

notes

about

model

compatibility

for,

and

this

certainly

affects

the

old

pbks.

F

You

know,

there's

you

know

in

order

to

be

in

this

business

at

all,

you

really

have

to

support

all

the

industry

standard

models,

and

you

know

there's

been

a

lot

of

work

under

the

compact

model

coalition

to

push

standardization,

but

for

a

lot

of

the

older

models,

some

of

which

I

think

perhaps

predate

the

CMC

effort.

The

standards

are

less

clear,

so

some

recent

examples

for

us

is,

you

know

we

have

the

spice

3

diode

in

Zeiss,

but

most

simulators

actually

have

added

stuff

to

the

spice.

F

3

diode,

like

you,

know,

sidewall

capacitance,

models

and

stuff

like

that.

So

we

had

to

add

those

another

example

would

be

the

Berkeley

beats

in

three

and

the

the

spice

three

code

that

came

from

Berkeley

is

not

quite

the

same

as

what's

in

most

simulators,

for

example,

there's

some

geometrical

parameters,

so

we

had

to

add

those

you

know,

so

those

sorts

of

things

come

up

and

that

that

can

be

a

bit

of

a

headache

to

deal

with,

but

we've

worked

on

it.

F

Let's

see

so

as

far

as

making

Zeiss

compatible

with

pdks

I

mean

an

awful

lot

of

our

Focus

has

just

been

on,

in

addition

to

the

parsing

issues

within

adding

features.

This

is

kind

of

a

there's,

a

very

long

list

of

things

that

we've

added

recently

and

there's

a

lot

of

stuff.

That's

in

progress

as

well

and

in

the

interest

of

time,

I

think

I'll,

move

on

to

the

next

slide

here.

F

F

Essentially

we're

just

planning

to

rewrite

to

replace

the

the

sections

that

have

to

do

with

Lexington

parsing,

with

something

that's

much

more

modern

and

we're

still

discussing

exactly

which

parser

generator

to

use

I

use,

flex

and

bison.

When

I

reread

the

expression

Library,

the

people

developing

xcm

have

used

Goose

Spirits,

so

those

are

probably

the

two

beating

candidates

for

that,

but

either

way

I

mean

language.

Grammars

are

usually

specified

in

a

fairly

common

format,

so

so

we

should

be

able

to

use

either

of

those

I

think.

F

Another

thing

we're

planning

to

do

as

part

of

this

is

to

create

an

abstract

data

model

which

sort

of

sits.

You

know

after

the

parsing

is

done,

and

that

abstract

data

model

allows

will

allow

us

to

basically

store

the

state

of

the

of

the

problem

in

a

binary

format,

and

so

that

that

should

enable

much

faster

simulations.

If

you,

if

you

don't

need

to

re-purse,

then

that

was

the

message

that

should

enable

much

faster

simulations.

F

The

Azure

data

model

is

also

part

of

our

plans

for

making

Zeiss

a

bit

more

Dynamic.

So

it's

easier

to

dynamically

change

things

in

the

in

the

circuit.

So,

let's

see

I

think

oh.

This

is

just

one

example

showing

that

size

gets

the

same

answer

as

a

commercial

tool

on

a

this

is

on

a

sorry,

ADC

circuit

using

Global

foundries,

12

nanometer.

You

know

we

have

a

lot

of

other

examples

like

this,

but

but

basically

we've

managed

to

make

that

work.

F

Our

hope

is

to

get

this

to

work

without

having

to

do

any

file

translation

at

all

right

now.

It

still

requires

some

file,

translation

and

yeah

I.

Think

that's

about

all

I

have

to

say

about

this.

I

mean

I.

I

could

talk

more

about

the

AI

stuff

if

anyone's

interesting,

I

have

a

I

have

a

slider

two

at

the

end

here,

but

I

don't

know

how

much

time

we

have

so

I'm

happy

to

take

questions.

F

F

So

I

guess

one

thing

I'll

mention

is

we're

doing

message

passing

so

we're

not

technically

doing

threading,

but

as

far

as

the

load

balance

goes,

I

mean

we've,

we've

kind

of

experimented

with

a

lot

of

things.

I

mean

for

at

least

for

our

message.

Passing

structure

we've

generally

found

that

it's

better

to

if

you're,

looking

at

a

very

heterogeneous

circuit

like

what

you

might

see

with

a

post

layout

circuit,

where

you

have

you

know

a

large

number

of

mosfets

and

also

a

large

number

of

parasitics.

F

If

the

circuits

rather

rather

homogeneous,

then

it

can

be

fine

to

to

group

them

by

type

as

long

as

as

long

as

they're,

you

know,

relatively

similar

expense,

I

mean

I'm

guessing

from

a

Threading

point

of

view.

I

mean

a

lot

of

times.

It's

it.

You

know

you're

looping

over

your

device

types

within

your

within

your

load,

phase

of

the

simulator

and

so

I

could

imagine.

F

G

H

F

H

K

H

F

F

Yeah,

let's

see

so

Muhammad's

question,

are

you

planning

to

integrate

the

translator

in

this

yeah?

I

mean

this.

Hopefully

my

my

talk

answered

that

question.

The

we're

planning

to

well

we're

basically

trying

to

recycle

the

grammars

that

we

develop

for

the

translator

and

then

use

those

grammars

with

to

set

up

a

modern

lecture

and

parser

in

the

directly

inside

of

size.

So

so,

hopefully,

a

year

from

now,

or

something

like

that,

it

won't

be

necessary

to

run

the

translator.

It'll

concise

will

just

run.

F

Let's

see

comment

about

tsmc.

Yes,

that's

my

experience

as

well:

Experience

open

source

fireworks,

so

I've

been

interacting

with

the

skywater

community

of

Fairmount

through

their

slack

Channel

and

so

on.

So

most

of

the

people

in

sky,

so

I

guess.

First

of

all,

the

version

of

skywater

that

I

have

used

was

I.

Think

the

one

Tim

Edwards

converted

to

run

in

g-spice

and

Angie

spice

is

not

100

the

same

as

ice,

but

it's

it's

closer

than

what

I've

experienced

with

a

lot

of

other

pdks.

F

F

F

F

F

The,

although

one

thing

I've

observed

with

agevice,

is

I

think

sometimes

they're

blazing

fast,

because

they've

taken

they've

taken

some

shortcuts.

My

experience

compared

to

Specter

is

that

we're

pretty

close

and

I

think

that's

well.

Hopefully,

nobody

from

Cadence

or

synopsis

is

going

to

yell

at

me

about

this,

but

but

my

experience

as

Specter

is

it

tends

to

be

a

bit

more

accurate.

A

spice,

let's

see

here

so

Tim

has

a

question:

is

the

Ivor

logo

simulation

considered

a

valid

way

to

do

so

and

that's

sort

of

so?

F

Let's

see

so,

we've

developed

a

mix,

a

mixed,

a

mixed,

a

mixed

signal,

interface

for

Zeiss

I,

kept

it

when

I

say

mixed.

We've

developed

a

mix

signal

interface

for

Zeus,

and

it's

been

called

from

a

variety

of

digital

tools.

You

can

call

it

from

bear

log,

but

it

doesn't,

but

we've

also

had

people

call

it

from

like

Pi,

HDL

and

stuff

like

that.

F

Let's

see

question

from

Kevin,

can

you

reach

the

Parables

into

this

The

Matrix

Hardware?

Yes,

that

there's

a

fair

amount

of

there's

fair

amount

of

tuning

that,

if

we're

running

truly

in

parallel,

where

we're

doing

a

true

sort

of

you

know,

especially

when

we're

doing

a

both

the

device

and

Matrix

part

of

the

problem.

In

parallel,

there's

quite

a

bit

of

two

anyone

can

do.

F

B

F

A

It's

quite

that

early

morning

in

New

Mexico,

so

maybe

one

more

cup

yeah

so

I

think

we

have

to

kind

of

speed

up

the

three

more

presentation.

Otherwise,

sorry

we

will

go

beyond

the

allocated

time.

We

will

have

meddy

talking

about

his

experience,

using

open

source

CDA

tools

for

free

pdk

of

skywater.

Then

we

have

Matthias

Booker.

A

He

will

give

an

update

on

akv

and

its

implementation

into

open

source

tools,

and

the

very

last

talk

today

will

be

by

team

talking

about

his

work

on

skywater,

Library

compatibility

with

spines

and

your

Eric.

Your

address

couple

of

points,

so

there

will

be

a

continuation

of

this

discussion

before

I

will

give

the

flow

to

maybe

a

Rob.

Can

you

assign

Matthias

boher

as

panelist?

He

will

talk

after

midi

about

AKB

model.

A

A

D

The

the

idea

behind

the

workshop

was

initially

to

talk

about

how

we

can

improve

the

technology

design

Loop

here

that

we

discussed

with

Rob

as

part

of

the

chips,

Alliance

activities

and

but

I'll

go

through

a

little

bit

of

the

work

I've

been

doing

and

how

I

encountered

the

open

source

tools

and

how

we're

trying

to

improve

them

as

we

go.

So

the

talk

is

lower

in

barriers

to

chip

design

using

openfa

stock.

D

Opener

Facebook

is

a

framework

that

started

or

it's

a

color

called

re

of

fa

stock,

which

is

a

DARPA

program.

So

let

me

just

move

to

the

next

slide.

So

if

I

talk

started

with

the

open

road

and

other

tools

as

part

of

the

idea

program,

I

think

size

is

part

of

it

as

well.

It's

a

military,

University

and

the

industry

effort.

We

are

part

of

chips

Alliance

and

we

teamed

up

with

arm

and

Virginia

too,

and

we

Professor

winsloff

was

the

lead

of

this

project.

D

Here

we

have

a

couple

talks

and

chips

Alliance,

so

you

can

go

and

take

a

look

at

them

and

I

listed

a

couple

of

papers

we

had

throughout

the

program

over,

of

course,

the

program

we

have

successfully

tipped

out

to

a

good

number

of

socs

from

gf12

to

TSM

c65.

We

demonstrated

some

of

them

at

the

URI

Summit,

and

that

was

successful

and

as

we

you

know,

as

the

open

source

pdk

was

released,

we

started

taping

out

more

chips

in

skywater

and

experimenting

more

more

stuff.

D

But

before

now

we

are

labeling

ourselves

as

open

fa

stock,

which

is

open

source

for

the

autonomous

SOC

synthesis

Tool.

We

are

part

of

chips,

Alliance

I'm,

sharing

the

analog

working

group

with

Rob

and

we're

discussing

a

lot

about

how

to

make

an

AUX

generation

and

custom

circuit

generation

more

automated,

using

open

source

tools.

Now

we

are

funded

by

Google

nest

and

a

couple

other

people

and

in

our

framework

we

are

not

only

using

a

service

approach

but

we're

using

tools

like

GDs

Factory,

and

sometimes

we

call

a

lion.

D

D

As

you

all

know,

it

must

have

it

is

custom

and

require

multiple

iterations

from

schematic

entry

to

layout,

then

simulation

and

so

forth.

The

digital

flow,

however,

is

fully

automated

right

and

we

can

call

it

a

grid

based

flow.

So

the

idea

here

is

to

basically

take

what

would

otherwise

be

a

full

custom,

anode

layout

and

shoehorn

it

into

the

cell

based

digital,

automated

design

flow

methodology,

which

is

very

amenable

to

the

available

logic,

synthesis

and

placed

in

route

tools,

be

it

proprietary

or

open

source.

D

So

you've

heard

that

a

few

times

now

we

use

a

cell

based

approach

and

the

idea

is

basically

to

divide

and

conquer

the

experience

we

had

with

a

fully

automated

or

Custom

Custom

based

analog

generators

is

that

they

it's

very

hard

to

bring

them

up,

and

it's

it's

a

pdk

dependent.

So

it's

really

hard

to

come

up

with

a

test

case

and

Port

it

to

a

new

technology.

D

This

could

be

either

from

a

traditional

Sanders

Library

or

a

library

that

has

been

augmented

with

a

couple

of

cells,

and

we

call

this

access

distance

as

auxiliary

cells,

Rock

cells,

we

so

to

demonstrate

our

demonstrate

our

framework.

We

did

notified

a

couple

circuit,

diagrams

or

generate

or

analog

blocks

that

we

have

published

in

isscc,

blsi,

basically,

Flagship

conference

circuit

conferences,

all

these

structures

have

been

taped

out

before

and

published.

D

So

these

are

Legacy

designs

that

have

proven

their

results

on

other

nodes

and

I

highlighted

in

blue

the

example

of

auxiliary

cells.

So

for

your

for

designs,

XR

adcs,

the

ldo

stamp

sensors,

PL

and

switch

cap

dc-dc

converters.

So,

each

time

the

analog

functions

is

either

an

auxiliary

and

header

cell

power

switch

a

flying

cap,

a

comparator,

and

so

it's

usually

a

12

below

transistor

block,

and

that

is

easier

to

tackle,

especially

if

it

is

if

it

defines

the

the

analog

functions

of

your

design.

D

D

They

they

usually

take

a

day

or

two

to

make.

Based

on

the

Innovation,

you

want

to

make-

or

let's

say,

you're

working

from

Skyward

130

to

Intel

16.

You

don't

have

any

native

transistor,

for

example,

or

any

other

exact

exotic

devices

so,

and

that

requires

you

to

rethink

a

little

bit

your

your

your

sensor

or

any

other

block.

So

in

that

case,

what

we

do

is

we

try

to

I

could

accommodate

the

auxiliary

cells.

D

You

know

in

a

way

we

can

pour

the

design

to

from

a

skywater

130

technology,

which

is

a

much

older

technology

to

refined

technology,

and

that

has

been

working

fine.

We

just

recently

taped

out

Intel

16

chip

that

that

is

showing

really

good

PEX

results,

but

in

general

these

are

the

the

auxiliary

cells.

They

look

like

standard

cells,

they

are

12

transistors

below.

We

try

to

use

different

Frameworks,

for

example,

aligned

from

Minnesota

and

Intel

to

basically

automate

this

last

piece

of

openfa

stock.

D

It

has

been

a

little

bit

challenging,

sometimes

especially

when

we

go

on

on

Advanced

notes,

but

it's

still

it's

still

working

for

some

of

our

auxiliary

cells.

So

it's

I

think

it's!

You

know.

It's

a

trade-off

on

how

much

you

want

automation

versus

Custom

Design,

but

the

idea

here

is

basically,

if

you

are

able

to

Define

different

auxiliary

cells,

you

are

you

you

go.

D

You

are

going

to

be

able

to

generate

thousands

of

designs

and

that's

that's

actually

very

interesting

in

especially

in

the

open

source

tools

where

you

don't

have

any

license

or

requirement,

or

you

don't

pay

for

your

license.

So

you

have,

you

can

generate

thousands

of

hundred

thousands

of

designs

and

basically

come

up

with

an

algorithm

to

decide

which

design

is

is

best.

So

I

think

this

is

very,

very

promising

and

we'll

see

much

more

of

it.

D

D

So

fsap

relies

on

a

set

of

proprietary

tools

and

wrapped

inside

the

Cadre

flow

developed

by

around

Professor

Ron

drezinski

from

Michigan,

and

it

isn't

as

abstracted

layer

over

the

closed

tools,

but

now

using

open

source

tools.

We

we

are

heavily

reliant

on

Open

Road

among

other

tools.

Also

GDs

Factory

I'll

I'll.

D

Try

to

discuss

that

later

in

this

presentation,

but

there's

a

couple

other

tools

like

your

CCBC

for

logic,

synthesis,

Sherlock,

uhdm,

plugins

integrated

by

and

micro

and

Google

for

system,

dialog

support,

magic

net,

gen

and

K

layout

thanks

to

team

Edwards

who's

here

and

also

NG

spice

excise.

So

we

don't

really

have

a

full

support

of

size

yet,

but

I

think

that's

one

of

the

action

items

we

have

for

the

next

months.

D

Here

you

require

100

complexity

and

compared

to

the

initial

version

we

had,

which

is

fa

stock

1.0,

which

is

standard

cell

only

based,

we

had

minimum

constraints

and

digital

compensation,

so

that

was

four

years

ago,

and

what

we

try

to

do

is

basically

include

some

partial

constraints

of

the

of

the

digital

flow.

Like

fencing,

non-default

rules

voltage

domains

to

basically

accommodate

some

of

the

needs

for

another

design,

and

when

we

do

that,

we

swing

back

into

the

middle,

where

we

we

can

see

that

we

can

get

the

best

of

both

words.

D

So,

in

fact,

in

using

our

sales

digital

approach,

we

are

in

reality

within

the

extreme

complexity

of

trying

to

take

all

taking

all

the

pdk,

DRC

rules

that

comes

in

with

full

custom,

automated

layout,

like

routing

and

active

layer,

drawing

also

with

the

rule

of

Dimension

Returns.

The

time

required

porting

to

a

new

pdk

or

even

a

new

design.

Topology

would

essentially

make

an

automated

flow

or

full

custom

analog

generator

too

costly

to

make

across

pdks

and

test

cases,

and

we

we

have

seen

precedence

in

that.

D

So

I

think

we

have

here

a

sweet

point

which

I

fundamentally

believe

we

could

push

more

to

the

left

using

open

source,

tooling

and

Automation

and

I'll

discuss

that

later.

In

this

presentation,

here's

a

few

examples

of

what

constraints

would

look

like

for

a

PLL

where

we

gave

extra

attention

to

the

dco

block.

We

are

using

Python

scripts

to

structure

the

placement

of

the

of

fine